# **Solutions - Midterm Exam**

(October 17<sup>th</sup> @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

### **PROBLEM 1 (24 PTS)**

a) Complete the following table. The decimal numbers are unsigned: (5 pts.)

| Decimal | BCD          | Binary   | Reflective Gray Code |

|---------|--------------|----------|----------------------|

| 27      | 00100111     | 11011    | 10110                |

| 57      | 01010111     | 111001   | 100101               |

| 133     | 000100110011 | 10000101 | 11000111             |

b) Complete the following table. The decimal numbers are signed. Use the fewest number of bits in each case: (15 pts.)

| REPRESENTATION |                    |                |                |  |

|----------------|--------------------|----------------|----------------|--|

| Decimal        | Sign-and-magnitude | 1's complement | 2's complement |  |

| -1             | 11                 | 10             | 1111           |  |

| -7             | 1111               | 1000           | 1001           |  |

| 11             | 01011              | 01011          | 01011          |  |

| -27            | <b>1</b> 11011     | 100100         | 100101         |  |

| 0              | 00                 | 1111           | 0              |  |

| -64            | 11000000           | 10111111       | 1000000        |  |

c) Convert the following decimal numbers to their 2's complement representations. (4 pts)

```

-27.25 \checkmark 26.5 +27.25 = 011011.01 \Rightarrow -27.25 = 100100.11 26.5 = 011010.1

```

## **PROBLEM 2 (17 PTS)**

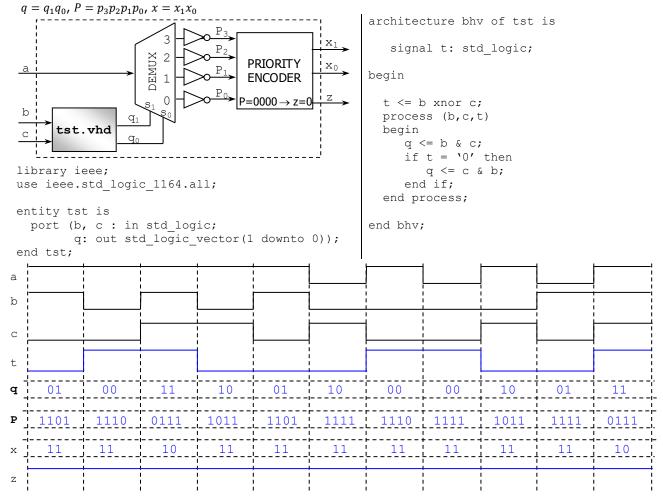

$\hbox{ \begin{tabular}{l} \hline $\bullet$ Complete the timing diagram of the following circuit. The VHDL code (tst.vhd) corresponds to the shaded circuit. } \\$

1

#### PROBLEM 3 (12 PTS)

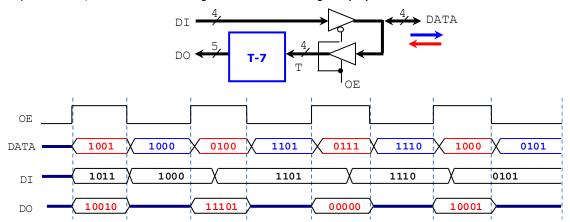

• Complete the timing diagram (signals *DO* and *DATA*) of the following circuit. The circuit in the blue box computes the signed operation T-7, with the result having 5 bits. T is a 4-bit signed (2C) number.

#### PROBLEM 4 (12 PTS)

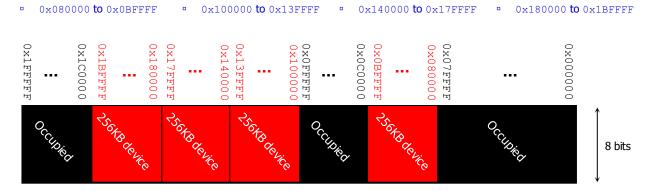

- The figure below depicts the entire memory space of a microprocessor. Each memory address occupies one byte.  $1KB = 2^{10}$  bytes,  $1MB = 2^{20}$  bytes,  $1GB = 2^{30}$  bytes

- ✓ What is the size (in bytes, KB, or MB) of the memory space? What is the address bus size of the microprocessor? (3 pts.)

Address Space:  $0 \times 000000$  to  $0 \times 1$  FFFFF. To represent all these addresses, we require 21 bits. So, the address bus size of the microprocessor is 21 bits. The size of the memory space is then  $2^{21} = 2$  MB.

✓ If we have a memory chip of 256 KB, how many bits do we require to address those 256 KB of memory? (1 pt.)

256 KB memory device:  $256KB = 2^{18}$  bits. Thus, we require 18 bits to address the memory device.

✓ We want to connect the 256 KB memory chip to the microprocessor. For optimal implementation, we must place those 256 KB in an address range where every address shares some MSBs. Provide a list of all the possible address ranges that the 256 KB memory chip can occupy. You can only use the non-occupied portions of the memory space as shown below.

#### PROBLEM 5 (18 PTS)

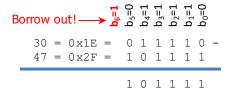

a) Perform the binary unsigned subtraction of these unsigned integers. Use the fewest number of bits n to represent both operators. Indicate every borrow from  $b_0$  to  $b_n$ . Determine whether we need to keep borrowing from a higher byte. (6 pts)  $\checkmark$  30 - 47

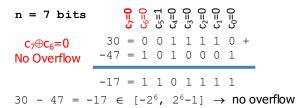

b) Perform the binary operation of these numbers, where numbers are represented in 2's complement. Indicate every carry from  $c_0$  to  $c_n$ . Use the fewest number of bits to represent the summands and the result so that overflow is avoided. (8 pts)  $\checkmark$  30 - 47

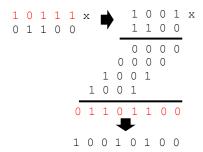

c) Perform binary multiplication of the following numbers that are represented in 2's complement arithmetic. (4 pts)  $\checkmark$  -9 x 12

# PROBLEM 6 (17 PTS)

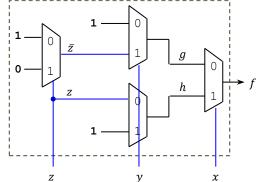

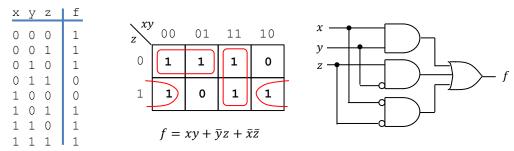

- Given the following Boolean function:  $f(x, y, z) = \prod M(3,4)$

- a) Provide the simplified expression for f and sketch this circuit using logic gates. (4 pts)

b) Implement the previous circuit using ONLY 2-to-1 MUXs (AND, OR, NOT, XOR gates are not allowed). (13 pts)

3

$$f(x,y,z) = \bar{x}f(0,y,z) + xf(1,y,z) = \bar{x}(\bar{y}z + \bar{z}) + x(y + \bar{y}z) = \bar{x}g(y,z) + xh(y,z)$$

$$g(y,z) = \bar{y}g(0,z) + yg(1,z) = \bar{y}(1) + y(\bar{z})$$

$$h(y,z) = \bar{y}h(0,z) + yh(1,z) = \bar{y}(z) + y(1)$$

Also:  $\bar{z} = \bar{z}(1) + z(0)$